# **OKI** Semiconductor

# MSM6388

# ADPCM SOLID STATE RECORDER

# GENERAL DESCRIPTION

The MSM6388 is a "solid-state recorder" LSI developed using ADPCM (Adaptive Differential Pulse Code Modulation) technology. When an external microphone, speaker driving amplifier, and OKI's original 1M-bit serial voice registers for ADPCM data storage are connected to the MSM6388, it can be used to record and play back voice or other sounds in a manner similar to that of a tape recorder.

### **FEATURES**

- 4bit ADPCM

- Built-in 12bit A/D converter

- Built-in 12bit D/A converter

- Built-in microphone pre-amplifier

- Built-in low pass filter (Attenuation characteristics -40dB/oct)

- Serial voice register 1Mbit serial voice register (MSM6389): Direct drive for 4 serial voice registers 512Kbit serial voice register (MSM6587): Direct drive for 1 serial voice register 256Kbit serial voice register (MSM6586): Direct drive for 1 serial voice register

- Serial Voice ROMs 1Mbit serial voice ROM (MSM6595-XXX) 2Mbit serial voice ROM (MSM6596-XXX) 3Mbit serial voice ROM (MSM6597-XXX)

- Maximum recording time: 262 seconds (when the sampling frequency is 4.0kHz)

- Power supply voltage: 5 V only

- 44 pin V 1 plastic QFP (QFP44-P-910-V1K)

# (WHEN USED AS A STANDALONE LSI)

- Oscillator frequency: 1.5MHz ~ 4MHz

- Sampling frequencies:

5.2, 5.9, 6.7kHz (when the oscillator operates at 1.5MHz) 3.9, 6.9, 7.8, 8.9 kHz (when the oscillator operates at 2.0MHz) 7.8, 13.9, 15.6kHz

(when the oscillator operates at 4.0MHz) Number of phrases to be recorded When one, two, or four serial voice

registers are connected, one, two, four or eight phrases can be selected. When three serial voice registers are connected, one, two, three, or six phrases can be

For the maximum recording time of each channel, the time divided by the number of phrases shall be assigned.

### (WHEN INTERFACED WITH A MICRO-CONTROLLER)

- Oscillator frequency: 1.5MHz ~ 4MHz (when a serial voice register is used) 1.5MHz~8MHz (when other memories are used)

- Sampling frequencies: 3.2kHz ~ 16kHz (when a serial voice register is used) 2.9kHz ~ 32kHz (when the other memories are used) 2.6, 2.9, 3.3, 5.2, 5.9, 6.7kHz (when the oscillator operates at 1.5MHz) 3.5, 3.9, 4.5, 6.9, 7.8, 8.9kHz (when the oscillator operates at 2.0MHz) 6.9, 7.8, 8.9, 13.9, 15.6, 17.8kHz (when the oscillator operates at 4.0MHz)

- eccorded

externally

externally

canonic recording time at each

channel can be set freely.

44 pin V1 plastic QFP (QFP44-P-910-V1K) The maximum recording time at each

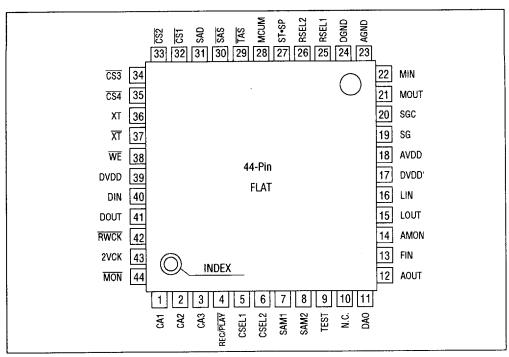

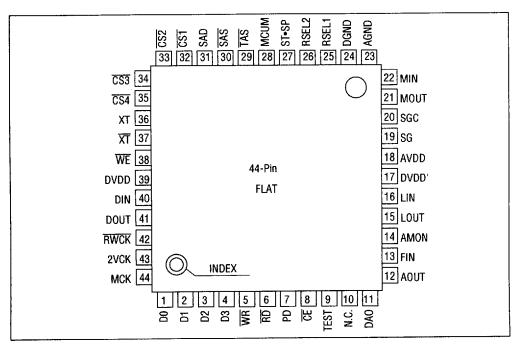

### **PIN LAYOUT**

• Stand-alone mode (MCUM pin = "L")

. Microcontroller interface mode (MCUM pin "H")

Note: Leave the NC pin open.

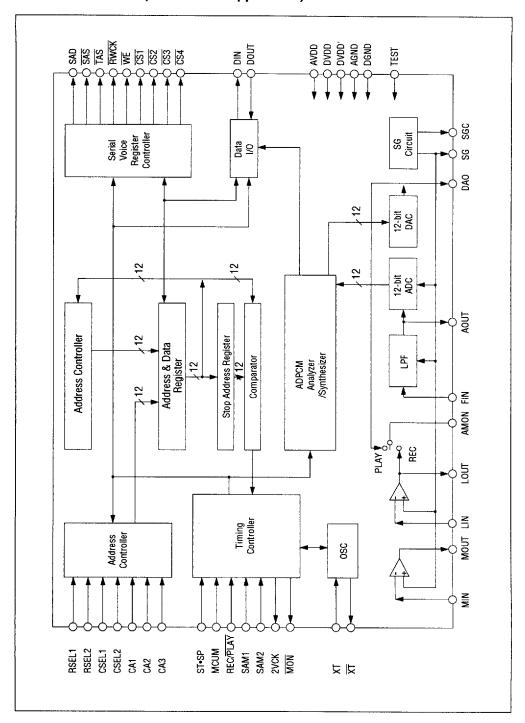

# **CIRCUIT DIAGRAM (Stand-alone application)**

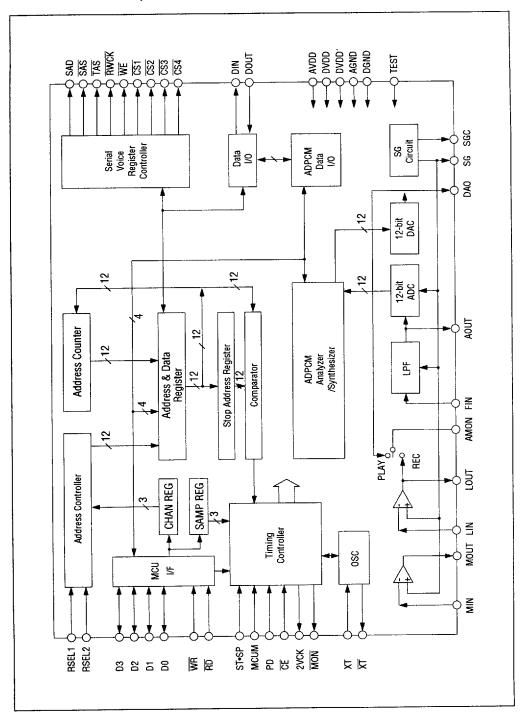

# **CIRCUIT DIAGRAM** (microcontroller interface application)

**■** 6724240 0016696 25T **■**

### **ELECTRICAL CHARACTERISTICS**

### Absolute Maximum Ratings

| Item                 | Symbol           | Conditions | Rating              | Unit |

|----------------------|------------------|------------|---------------------|------|

| Power supply voltage | VDD              | Ta = 25°C  | -0.3 ~ +7.0         | ٧    |

| Input voltage        | Vin              | Ta = 25°C  | -0.3 ~ VDD +0.3     | V    |

| Storage temperature  | T <sub>stg</sub> | _          | −55 ~ + <b>1</b> 50 | °C   |

### Operating Range

| Item                        | Symbol | Conditions       | Range       | Unit |

|-----------------------------|--------|------------------|-------------|------|

| Power supply voltage        | VDD    | DGND = AGND = 0V | +3.5 ~ +5.5 | ٧    |

| Operating temperature range | Top    |                  | -40 ~ +85   | ℃    |

| Oscillator frequency        | fosc   | _                | 1.5 ~ 8     | MHz  |

#### • DC Current Characteristics

(DVDD=AVDD=DVDD'=4.5~5.5V, DGND=AGND=0V, Ta=-40~+85°C)

| Item                        | Symbol           | Conditions                  | Min.    | Тур. | Max. | Unit |

|-----------------------------|------------------|-----------------------------|---------|------|------|------|

| High input voltage (Note 1) | V <sub>IH1</sub> |                             | 3.6     | _    | _    | ٧    |

| High input voltage (Note 2) | V <sub>IH2</sub> | _                           | 0.8×VDD |      |      | ٧    |

| Low input voltage (Note 1)  | V <sub>IL1</sub> | _                           | _       | _    | 0.8  | V    |

| Low input voltage (Note 2)  | V <sub>IL2</sub> | _                           | _       |      | 0.8  | ٧    |

| High output voltage         | VoH              | l <sub>OH</sub> = -40μA     | 4.2     | _    | _    | ٧    |

| Low output voltage          | V <sub>OL</sub>  | I <sub>OL</sub> = 2mA       | _       |      | 0.45 | ν    |

| High input current (Note 3) | l <sub>IH1</sub> | V <sub>IH</sub> = VDD       | _       | _    | 10   | μA   |

| High input current (Note 2) | I <sub>IH2</sub> | V <sub>IH</sub> = VDD       | _       | _    | 20   | μА   |

| High input current (Note 4) | liH3             | V <sub>IH</sub> = VDD       | 20      |      | 400  | μA   |

| Low input current (Note 1)  | I <sub>IL1</sub> | V <sub>IL</sub> = GND       | -10     | _    | _    | μА   |

| Low input current (Note 2)  | l <sub>IL2</sub> | V <sub>IL</sub> = GND       | -20     | _    | -    | μA   |

| Operating current (1)       | IDD              | fosc = 4.0MHz, without load | _       | 5    | 10   | mA   |

| Operating current (2)       | IPD              | At power down, without load |         |      | 10   | μA   |

Note 1: Applies to the input pins excluding the XT pins.

Note 2: Applies to the XT pin.

Note 3: Applies to the pins not connected to pull-down resistors and excluding the XT pin.

Note 4: Applies to the pins connected to pull-down resistors and excluding the XT pin.

# • Analog Characteristics

(DVDD=AVDD=DVDD'=4.5~5.5V, DGND=AGND=0V, Ta=-40~+85°C)

| Item                                  | Symbol           | Conditions                 | Min. | Тур. | Max.  | Unit |

|---------------------------------------|------------------|----------------------------|------|------|-------|------|

| Relative DA output error              | I VDAE I         | Under no load              |      | _    | 10    | m۷   |

| DA output impedance                   | RDAO             | <del>_</del>               | 12   | 20   | 28    | kΩ   |

| Fin input voltage                     | Vein             |                            | 1    | _    | VDD-1 | ٧    |

| Fin input impedance                   | R <sub>FIN</sub> | _                          | 1    |      | _     | MΩ   |

| Operational amplifier open loop gain  | Gop              | f <sub>IN</sub> = 0 ~ 4kHz | 40   | -    |       | dB   |

| Operational amplifier input impedance | RINA             | _                          | 1    |      | _     | MΩ   |

| Operational amplifier load resistance | ROUTA            | _                          | 200  |      |       | kΩ   |

| AOUT load resistance                  | RAOUT            | _                          | 50   | _    | _     | kΩ   |

#### . A.C. Characteristics

# 1. Stand-alone Application

(DVDD=AVDD=DVDD'=4.5~5.5V, DGND=AGND=0V, Ta=-40~+85°C, fosc=2.048MHz, and f<sub>sam</sub>=8.0kHz)

| Item                                                                  |   | Symbol       | Min. | Тур. | Max. | Unit |

|-----------------------------------------------------------------------|---|--------------|------|------|------|------|

| ST-SP pulse width                                                     | * | tstp         | 70   | _    |      | ms   |

| MON clock output time during recording                                | * | talw         | _    | 4    | _    | S    |

| MON clock cycle during recording                                      | * | talc         | _    | 256  | _    | ms   |

| Time before starting record or playback after start pulse input       | * | tana         | _    | 260  |      | ms   |

| Time required for AOUT/DAOUT output to reach 1/2 VDD from GND level   | * | <b>t</b> DAR | _    | 44   | _    | ms   |

| Time required from the end of playback to power down state            | * | <b>t</b> DAF |      | 128  |      | ms   |

| Time required for voice to be output again during a repeated playback | * | tms          | _    | 1    |      | ms   |

Note:\* Duration of items with "\*" is proportional to the cycle of the sampling frequency f<sub>sam</sub>.

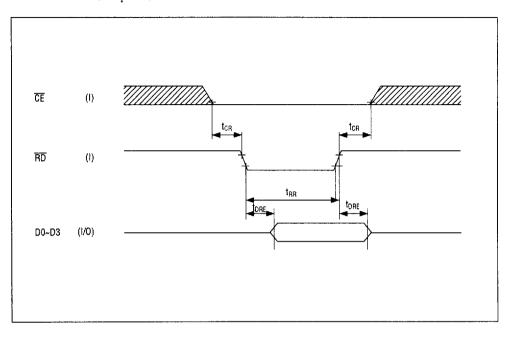

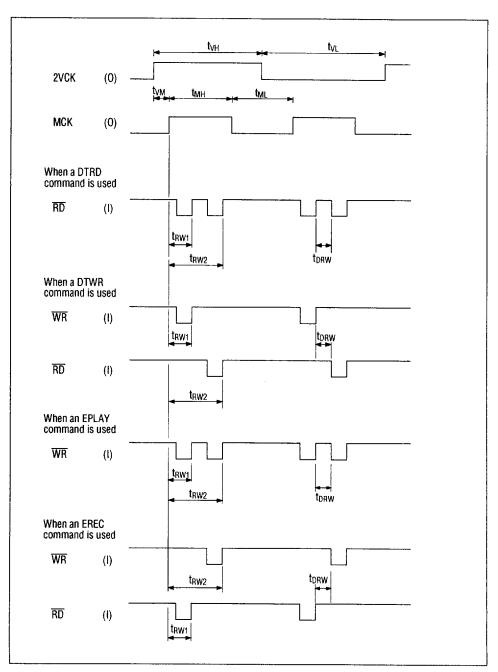

#### Microcontroller Interface Application 2.

(DVDD=AVDD=DVDD'=4.5~5.5V, DGND=AGND=0V,  $Ta=-40\sim+85$ °C,  $f_{OSC}=2.048MHz$ , and  $f_{sam}=8.0kHz$ )

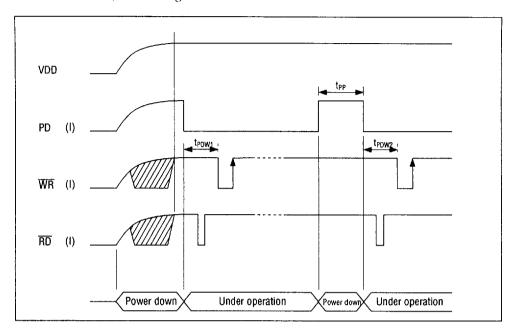

| ltem                                                     | Symbol            | Min. | Тур. | Max. | Unit |

|----------------------------------------------------------|-------------------|------|------|------|------|

| PD pulse width                                           | tpp               | 2    | _    |      | μs   |

| Time from PD release to WR pulse input (Note 2)          | t <sub>PDW1</sub> | 10   |      |      | ms   |

|                                                          | <b>t</b> PDW2     | 2    | _    | _    | μs   |

| RD pulse width                                           | t <sub>RR</sub>   | 200  | _    |      | ns   |

| CE setup and hold times to RD                            | t <sub>CR</sub>   | 50   |      |      | ns   |

| Time from RD fall to data valid                          | t <sub>DRE</sub>  |      | 60   | 150  | ns   |

| Time from RD rise to data float                          | t <sub>DRF</sub>  | _    | 40   | 90   | ns   |

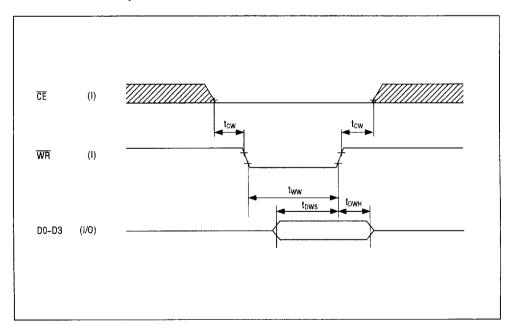

| WR pulse width                                           | tww               | 200  | _    | _    | ns   |

| CE setup and hold times to WR                            | t <sub>cw</sub>   | 50   | _    | _    | ns   |

| Data setup time to WR rise                               | t <sub>DWS</sub>  | 100  | _    | _    | ns   |

| Data hold time to WR rise *                              | t <sub>DWH</sub>  | 30   |      | _    | ns   |

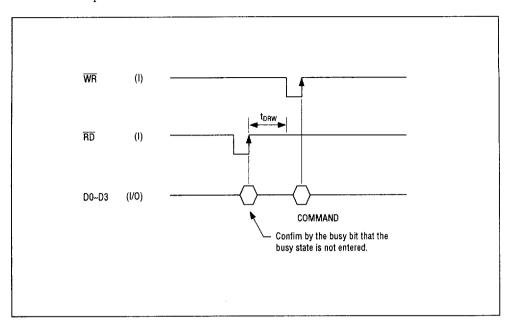

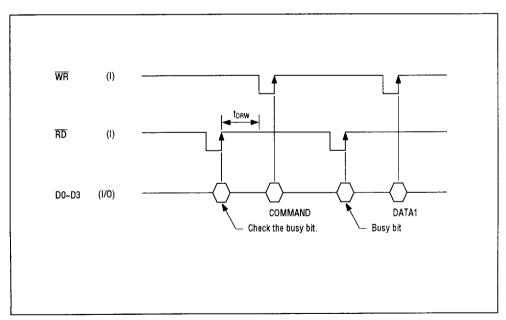

| RD and WR disable time *                                 | t <sub>DRW</sub>  | 250  | _    | _    | ns   |

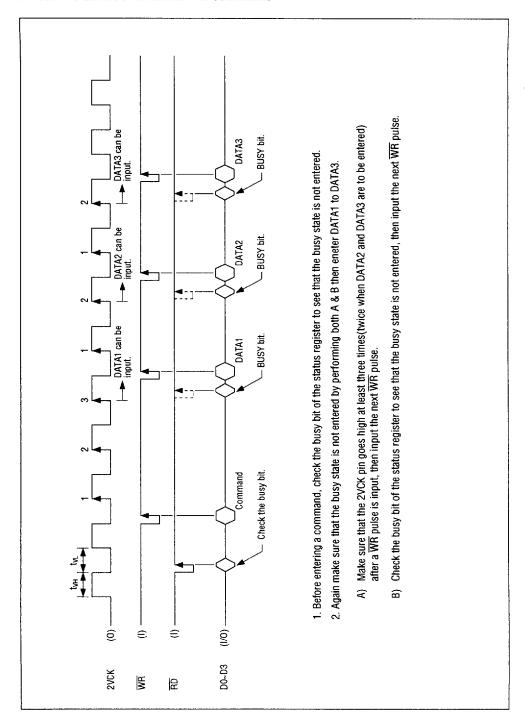

| 2VCK "H" level time *                                    | t∨H               |      | 125  | _    | μs   |

| 2VCK "L" level time *                                    | t <sub>VL</sub>   | _    | 125  | _    | μs   |

| MCK "H" level time *                                     | <b>t</b> мн       | _    | 62.5 |      | μs   |

| MCK "L" level time                                       | t <sub>ML</sub>   | _    | 62.5 | _    | μs   |

| Time required from 2VCK rise to MCK rise                 | t <sub>VM</sub>   | -    | 23.4 | _    | μs   |

| Time required from MCK rise to the rise of the *         | <b>A</b>          | 2.50 |      |      |      |

| first shot of RD and WR pulse                            | tRW1              | 250  | _    | -    | ns   |

| Time required from MCK rise to the rise of the           |                   |      |      | 00.5 |      |

| second shot of $\overline{RD}$ and $\overline{WR}$ pulse | tRW2              | _    | -    | 62.5 | μs   |

Note 1: \* Duration of items marked with "\*" is proportionate to the cycle of the sampling frequency fsam.

Note 2: The oscillation stable time is added to t<sub>PDW1</sub>.

The oscillation stable time is a few tenths of a ms for crystal oscillators and is a few hundredths of a ms for ceramic oscillators.

#### **TIMING CHARTS**

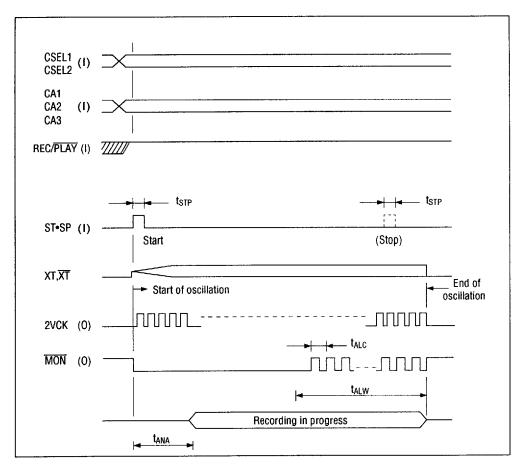

### Standalone Application

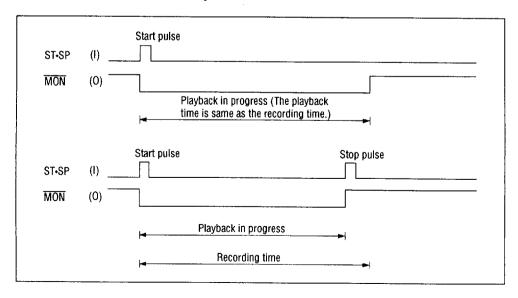

### Recording timing

Note: When the remaining capacity of available memory of the selected channels falls to 128K-bit (last four seconds) during recording, a 4Hz clock is output from the  $\overline{\text{MON}}$  pin. (f<sub>sam</sub>=8kHz)

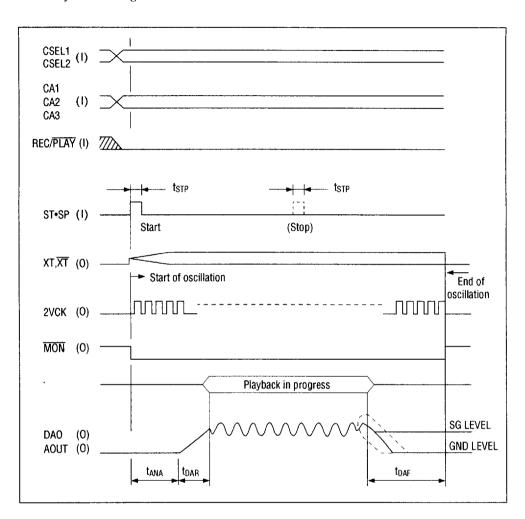

### 2. Playback Timing

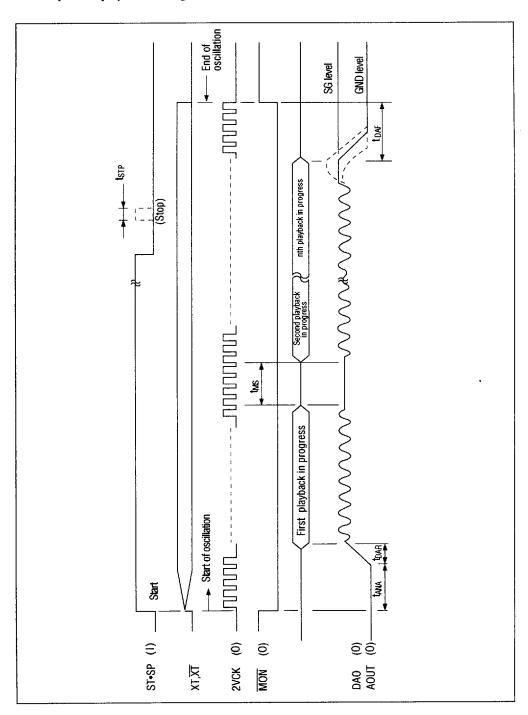

# 3. Repetitive playback timing

**Note:** Playback is peformed repeatedly while the ST•SP pin is maintained at the high level. When the pin goes low then a Stop pulse is input or playback proceeds up to the end of the channel memory and is stopped.

518

# • Microcontroller interface application

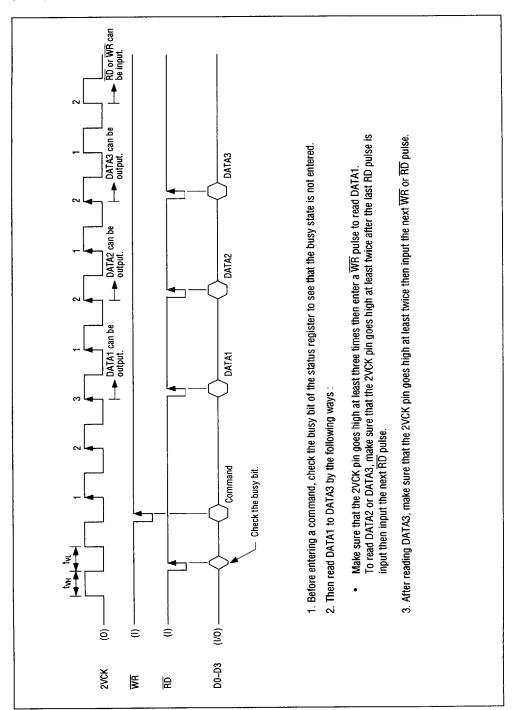

# 1. Data Read (RD pulse)

# 2. Data Write (WR pulse)

3. How to Input One-nibble Commands, NOP, INIT, PLAY, REC, START and STOP

4. How to Input Two-nibble Commands, SAMP and CHAN

### 5. How to Enter STWR and SPWR Commands

#### 6. How to Enter STRD and SPRD Commands

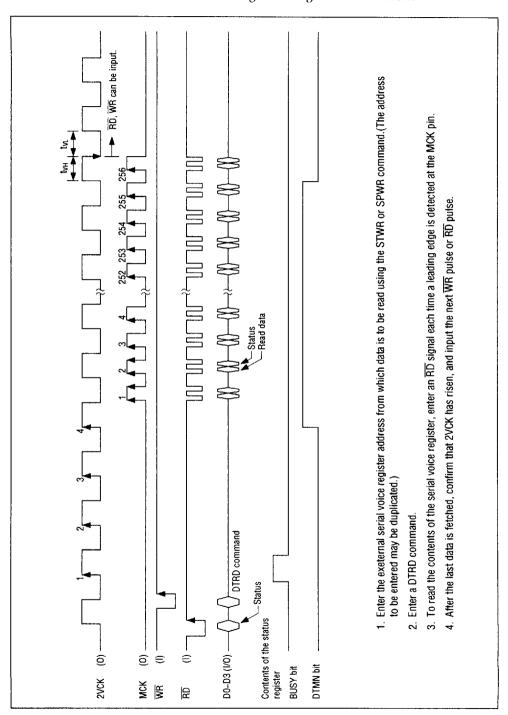

# 7. How to Read Data from a Serial Voice Register Using a DTRD Command

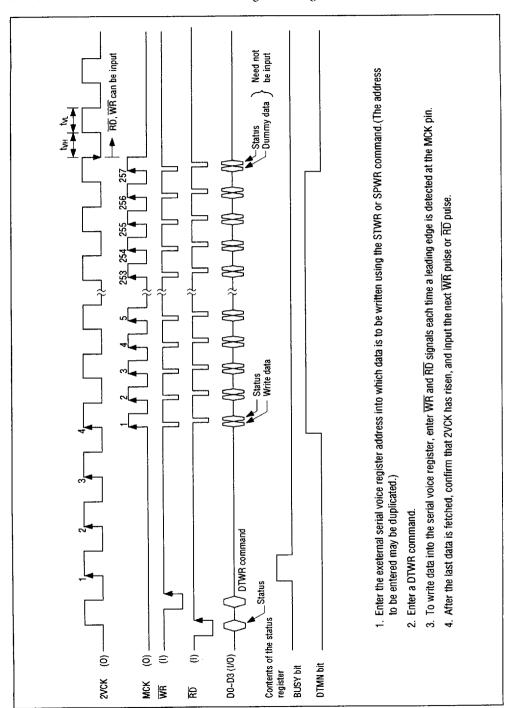

8. How to Write Data into a Serial Voice Register Using a DTWR Command

# ■ 6724240 0016708 8T1 **■**

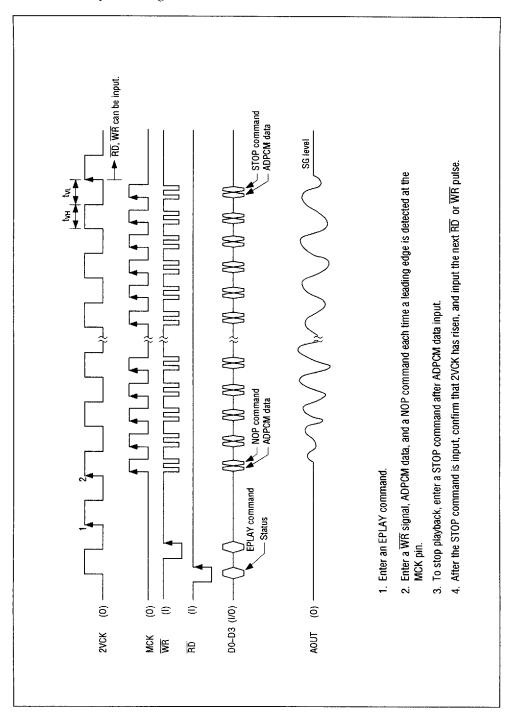

# 9. How to Playback Using an EPLAY Command

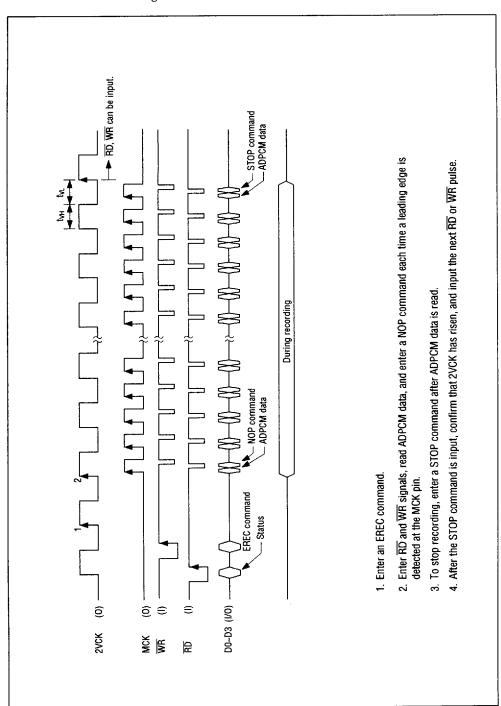

# 10. How to Record Using an EREC Command

How to enter WR and RD signals in one sampling cycle when a DTRD, DTWR, EPLAY, or EREC command is used

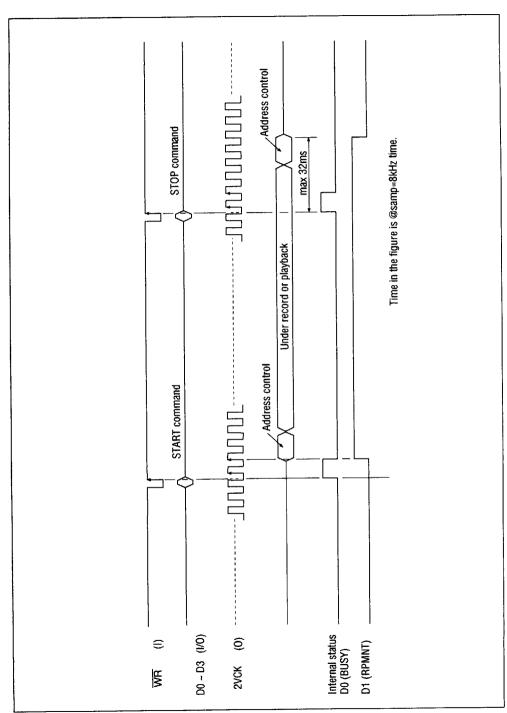

# 12. Start and Stop of Playback by START Command and STOP Command

**-** 6724240 0016712 222 **-**

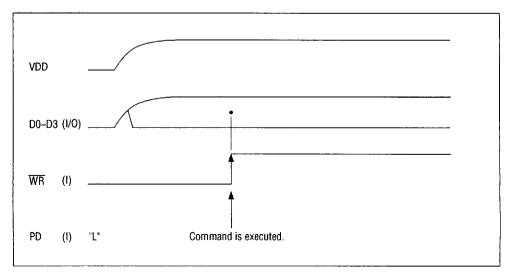

### 13. Power down, reset timing

Power-down state occurs by inputting "H" level to PD pin and at the same time, the control circuit is reset. However, this is not a forced reset pin, but is invalid during performing DTRD and DTWR commands, and during recording and playback.

After power-on, input "H" level to PD pin

until the VDD voltage is stabilized. For instance, after power is put on as illustrated below, the "H" edge is generated at  $\overline{\text{WR}}$  pin and then the commands of the contents for  $D_0 \sim D_3$  pins are executed. At this time, if a START command or the DTRD and DTWR commands are carried out, the reset by PD pin becomes impossible.

# **FUNCTION OF PINS**

# • Pins for Both Stand-alone and Microcontroller Interface Application

| Pin Name | 1/0 | Function                                                                     |

|----------|-----|------------------------------------------------------------------------------|

| DVDD     | _   | Digital power supply pin                                                     |

| AVDD     | _   | Analog power supply pin                                                      |

| DVDD'    | -   | Power supply pin                                                             |

| DGND     | _   | Digital ground pin                                                           |

| AGND     | _   | Analog ground pin                                                            |

| SGC      | 0   | Outputs the reference voltage (signal ground (SG)) of the analog             |

| SG       |     | circuit. A capacitor is connected between this pin and the GND               |

|          |     | pin to stabilize the voltage.                                                |

| MIN      | ı   | Input pin that inverts the input to the built-in operational amplifier.      |

| LIN      |     | Non-inverted pins are connected to the SG internally.                        |

| MOUT     | 0   | MOUT is an output pin of the built-in operational amplifier                  |

| LOUT     |     | corresponding to the MIN input pin. The LOUT output pin corresponds          |

|          |     | to the LIN input pin.                                                        |

| AMON     | 0   | Connected to the LOUT pin during recording and to the DA converter           |

|          |     | output pin during playback. Connect to the FIN input pin of the built-in     |

|          |     | amplifier.                                                                   |

| FIN      | ı   | Input pin ot the built-in low-pass filter                                    |

| AOUT     | 0   | Analog voice output pin                                                      |

| DAO      | 0   | Output pin of the built-in 12-bit DA conveter                                |

| SAD      | 0   | (Serial Address Data) Connected to the SAD pin of the serial voice           |

|          |     | register to output the first address for read/write operation.               |

| SAS      | 0   | (Serial Address Strobe) Clock pin connected to the SAS pin of the            |

|          |     | serial voice register to write serial addresses                              |

| TAS      | 0   | (Transfer Address Strobe) Connected to the TAS pin of the serial voice       |

|          |     | register. The TAS pin sets serial addresses to the internal address          |

|          |     | counter of the serial voice register.                                        |

| RWCK     | 0   | (Read/Write Clock) Clock terminal connected to the RWCK pin of the serial    |

|          |     | voice register to read data from and write it into the serial voice register |

| WE       | 0   | (Write Enable) Output pin connected to the WE pin of the serial voice        |

|          |     | register to select the write or read mode                                    |

| DIN      | 0   | (Data Input) Connected to the DIN pin of the serial voice register to        |

|          |     | outputwrite data                                                             |

| Pin Name | 1/0                                                          | Function                                                                               |  |

|----------|--------------------------------------------------------------|----------------------------------------------------------------------------------------|--|

| DOUT     | I (Data Output) Connected to the DOUT pin of the serial void |                                                                                        |  |

|          |                                                              | fetch read data.                                                                       |  |

|          |                                                              | When used at stand-alone mode, insert a pull-down register                             |  |

|          |                                                              | of about 100k $\Omega$ between DOUT pin and GND.                                       |  |

| CS1      | 0                                                            | (Chip Select) Connected to the $\overline{\text{CS}}$ pin of the serial voice register |  |

| CS2      |                                                              |                                                                                        |  |

| CS3      |                                                              |                                                                                        |  |

| CS4      |                                                              |                                                                                        |  |

| MCUM     |                                                              | Determines whether the LSI is used in stand-alone mode or connected                    |  |

|          |                                                              | to a microcontroller interface.                                                        |  |

|          |                                                              | High level: Connected to a microcontroller interface                                   |  |

|          |                                                              | Low level: Used as a stand-alone LSI                                                   |  |

| RSEL1    | ı                                                            | (Register Select) Selects the number of serial voice registers. For                    |  |

| RSEL2    |                                                              | details, see Explanation of Functions described later.                                 |  |

| 2VCK     | 0                                                            | Outputs a clock at a frequency half the sampling frequency. Used as                    |  |

|          |                                                              | a synchronizing clock when the LSI is connected to a microcontroller                   |  |

|          |                                                              | interface.                                                                             |  |

| XT       | ı                                                            | Connected to the resonator. When an external clock is used, clock                      |  |

|          |                                                              | pulses are supplied through this pin. When the power goes down,                        |  |

|          |                                                              | it is set to the ground level.                                                         |  |

| XT       | 0                                                            | Connected to the resonator. When an external clock is used, it must                    |  |

|          |                                                              | be left open.                                                                          |  |

| TEST     | ı                                                            | LSI test pin. Connected to a pull-down resistor in the LSI. This pin                   |  |

|          |                                                              | must be set at the low level.                                                          |  |

# • Stand-alone Application

| Pin Name | 1/0 |                                                                         | Function                                                                 |               |                             |                 |      |

|----------|-----|-------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------|-----------------------------|-----------------|------|

| CSEL1    | 1   | Selects the num                                                         | Selects the number of phrases to be recorded. For details, see           |               |                             |                 |      |

| CSEL2    |     | Explanaiton of F                                                        | Explanaiton of Functions described later.                                |               |                             |                 |      |

| CA1      | 1   | Specifies a char                                                        | Specifies a channel. For details, see Explanation of Functions described |               |                             |                 |      |

| CA2      |     | later.                                                                  |                                                                          |               |                             |                 |      |

| CA3      |     |                                                                         |                                                                          |               |                             |                 |      |

| SAM1     | 1   | Sample frequen                                                          | cy selection.                                                            | The relation  | ships betwe                 | en the oscillat | or   |

| SAM2     |     | frequency (fosc                                                         | ) and the san                                                            | npling freque | ency (f <sub>sam</sub> ) ai | e as follows    |      |

|          |     | (the frequencies                                                        | s in parenthe                                                            | ses are meas  | sured at fosc               | =2.048MHz):     |      |

|          |     | ,                                                                       |                                                                          |               |                             |                 |      |

|          |     | SAM2                                                                    | L                                                                        | L             | Н                           | Н               |      |

|          |     | SAM1                                                                    | L                                                                        | Н             | L                           | Н               |      |

|          |     | f <sub>sam</sub>                                                        | f <sub>osc</sub><br>512                                                  | 10SC 288      | f <sub>0SC</sub> 256        | 10sc 224        |      |

|          |     |                                                                         | (4.0kHz)                                                                 | (7.1kHz)      | (8.0kHz)                    | (9.1kHz)        |      |

| REC/PLAY |     | Selects the reco                                                        | ording mode                                                              | when the inp  | out is at the h             | igh level or th | e    |

|          |     | playback mode                                                           | when it is at                                                            | the low level | l.                          |                 |      |

| ST•SP    | I   | Allows the start                                                        | ing or ending                                                            | g of recordin | g or playbac                | k to be         |      |

|          |     | commanded by inputting a high pulse. It also allows repetitive playback |                                                                          |               |                             |                 |      |

|          |     | when the high I                                                         | evel is maint                                                            | ained during  | playback.                   |                 |      |

| MON      | 0   | Set at the low le                                                       | nen the remain                                                           | ing           |                             |                 |      |

|          | -   | memory capaci                                                           | ty of the chai                                                           | nnel is almos | t full this ni              | n nutnuts a clo | ock. |

# Microcontroller Interface Application

| Pin Name | 1/0 | Function                                                               |

|----------|-----|------------------------------------------------------------------------|

| D3       | 1/0 | Connects to a bidirectional data bus to transfer data and commands     |

| D2       |     | to and from an external microcontroller.                               |

| D1       |     |                                                                        |

| D0       |     |                                                                        |

| WR       | 1   | Write pulse input pin to write commands or data                        |

| RD       | l   | Read pulse input pin to read status or data                            |

| PD       | I   | When a high Power Down is input, the LSI enters the power down         |

|          |     | state.                                                                 |

| CE       | I   | When a high Chip Enable is input, the write pulse WR and read pulse    |

|          |     | RD cannot be accepted and pins D0 to D3 go high impedance.             |

| MCK      | 0   | Outputs a synchronizing clock when ADPCM data is tranferred directly   |

|          |     | to and from a microcontroller by an EREC or EPLAY command or when      |

|          |     | data is transferred directly between a microcontroller and serial      |

|          |     | registers by a DTWR or DTRD command.                                   |

| ST•SP    | l   | Not used. Since it is connected to a pull-down resistor in the LSI, it |

|          |     | must be set at the low level.                                          |

#### **EXPLANATION OF FUNCITONS**

### Recording time and memory capacity

The recording time depends on the capacity of the external serial voice register, sampling frequency, and ADPCM bit length. The relationship between these factors is represented by the following expression:

$$\frac{\text{Recording}}{\text{time}} = \frac{1.024 \times \text{memory capacity (K-bit)}}{4(\text{kHz}) \times 4(\text{bit})} (S)$$

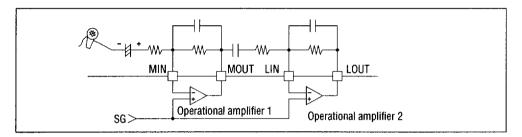

### Analog input amplifier circuit

The LSI described in this manual has two operational amplifiers configured as a microphone preamplifier. The LSI is provided with pins for inverted input and output of each amplifier.

The noninverted input pins are connected to the signal ground (SG) used as the analog circuit reference voltage in the LSI. For amplification, an inverted amplifier circuit is formed. The gain of the amplifier can be adjusted by an external resistor.

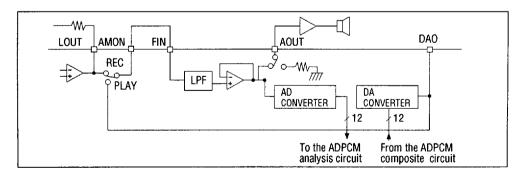

### Connection of the low-pass filter circuit periphery

In the LSI, the amplifier circuit from the LOUT pin is connected to the AMON pin. During playback, the D/A converter output from DAO pin is connected to the AMON pin.

The LSI incorporates a fourth-order lowpass filter employing switched capacitor filter technology. Input is provided to the lowpass filter through the FIN pin. Therefore, the AMON pin is connected to the FIN pin directly.

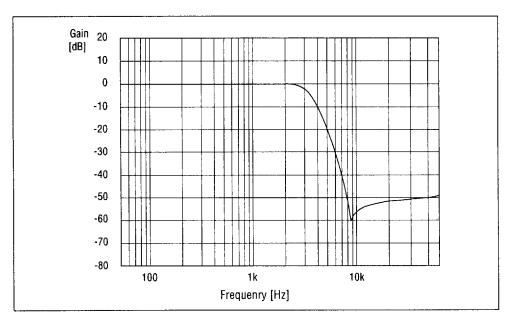

#### · LPF characteristics

The LPF attentuation characteristics of this LSI are about -40dB/oct, and the cutoff frequency and frequency characteristics vary in proportion to the sampling frequency (fsam).

The cutoff frequency is about 3.2kHz when the sampling frequency is 8kHz.

The LPF frequency characteristics are shown below.

LPF Frequency Characteristics (f<sub>sam</sub>=8.0kHz)

#### Analog (voice) output

During playback this signal is output from the AOUT pin. Connect the output to a speaker through a power amplifier suitable for driving speakers of from 4 to  $16\Omega$  impedance.

The amplitude of the built-in 12bit D/A converter output, provided from the DAO pin, is a maximum of  $4095/4096 \times VDD$ . When not using the built-in low-pass filter, connect it to the DAO pin.

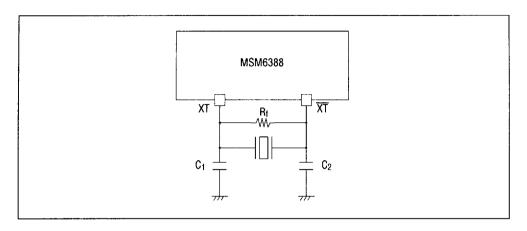

### · How to connect the oscillator

The ceramic oscillator or crystal oscillator are connected to the XT and  $\overline{XT}$  terminals as shown below.

For reference, when the ceramic oscillator manufactured by KYOCERA or Murata Seisakusho is connected, the optimum load capacity value is as shown below.

| Ceramic oscillator |             |                           | Optimu<br>capaci | Feedback resistance |                     |               |

|--------------------|-------------|---------------------------|------------------|---------------------|---------------------|---------------|

| Model Name         |             | Model Name Frequency (Hz) |                  | C <sub>1</sub> (PF) | C <sub>2</sub> (PF) | $R_f(\Omega)$ |

| - ····             | CSA 1.500MK | 1.5M                      |                  | 30                  |                     |               |

| Murata             | CSA 2.00MG  | 2.0M                      | 00               |                     | (414)               |               |

| Seisakusho         | CSA 4.00MG  | 4.0M                      | 30               |                     | (1M)                |               |

|                    | CSA 8.00MT  | 8.0M                      |                  |                     |                     |               |

|                    | KBR 2.0MS   | 2.0M                      |                  |                     |                     |               |

| KYOCERA            | KBR 4.0MS   | 4.0M                      | 33               | 33                  | _                   |               |

|                    | KBR 8.0MS   | 8.0M                      |                  |                     |                     |               |

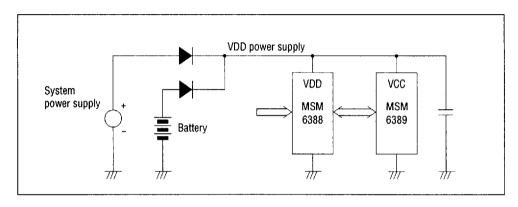

### Battery back up of the 1M serial voice registers

When backing up the 1M serial voice register, back up MSM6388 at the same time. When backing up only a 1M serial voice register, the bootstrap function works and cannot be played back when the power supply is turned on.

An example of the circuit that obtains VDD supply power is shown below. In this case, VDD and VDD at back up is about respectively 0.7V lower than the system power

supply voltage and battery voltage due to the drop of the diode forward voltage.

The non-volatile battery backup circuit has the following conditions:

- When the VDD supply voltage is dropped, the H level of the input signal must not exceed VDD +0.3V.

- (2) VDD at the time of backup must be in the range of 3.5 to 5.5V.

Figure: Example of Battery Backup Circuits of MSM6388 and MSM6389

# Battery driving

An example of the estimated battery life when a +4.5V power supply is operated by serially connecting four MSM6389's, MSM6388, speaker driver, and speaker (example of application circuit and circuit diagram 1) with three dry cell batteries is shown below.

For the current capacity, assume a 3 SUM Mn dry cell battery (R6P), and the capacity up to the drop of the voltage to 1.2V of about 600 mAhrs. When the section consuming current in Circuit Diagram 1 is divided into the MSM6388, four MSM6389's, amplifier, and speaker, the current consumed in each section is as shown in the table below, corresponding to each operation mode.

|                    | Operation mode |             |                   |  |  |

|--------------------|----------------|-------------|-------------------|--|--|

| Circuit            | At recording   | At playback | At data retention |  |  |

| MSM6388            | 5mA            | 5mA         | _                 |  |  |

| MSM6389 (four)     | 1mA            | 1mA         | 30μA × 4 = 120μA  |  |  |

| Amplifier, speaker | _              | 20mA        | _                 |  |  |

| Total              | 6mA            | 26mA        | 0.12mA            |  |  |

When the recording time per day is 4 minutes, playback time 4 minutes, and the data retention time is 10 hours as the standard time, the current consumption per day is:

At recording:

$6\text{mA} \times \frac{4}{60} = 0.4\text{mAhrs}$

At playback:

$26\text{mA} \times \frac{4}{} = 1.73\text{mAhrs}$

At data retention: 60

$0.12mA \times 10 = 1.2mAhrs$

The total consumption per day is 3.3 mAhrs. In other words, if a battery of 600 mAhrs is used for the capacity, a service life of 600 mAhrs/3.3 mAhrs = 180 days is provided. The battery can be used for six months without replacement.

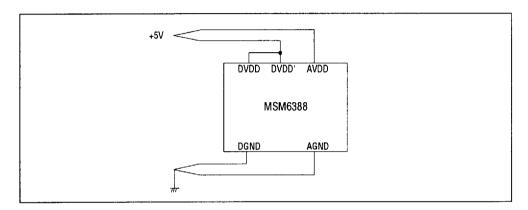

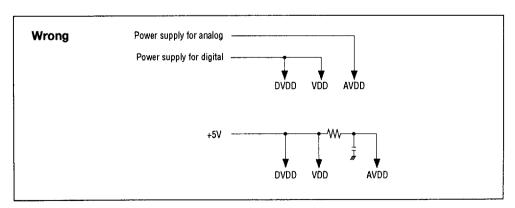

### Power supply wiring

Supply the power supply of this LSI from the same power source as illustrated below, while separating the analog portion and logic portion in wiring.

If the analog portion and logic portion are suppied from a separate power source, make sure the voltage difference between both power sources does not exceed ±3 volts or latch-up may occur.

#### Increasing Power supply

The internal power-on reset circuit of MSM6388 requires that the common supply voltage to AVDD, DVDD, and DVDD' is increased from 0 to +3.5V exponentially and

smoothly within 20ms. If the voltages of less than 20ms is provided or if by accident the voltage drops once during the increasing period the MSM6388 may behave unpredictable.

#### Power OFF/ON

During an interval between a power OFF and a subsequent power ON, the level on VDD input must be less than 0.05V at the

instant of a new power ON. Also, this measure accounts for the nature of the internal power-on reset circuit.

### Operations in the standalone application

#### Power down function

When the LSI is not recording or playing back data, the power down function is enabled and oscillation is stopped. At power down when an external clock is used, be sure to set the XT pin to the ground level to lower current consumption.

2. Oscillator frequency and sampling frequency

The oscillator frequency fosc can be used between 1.5MHZ and 4MHZ. The sampling frequency (fsam) is related to the oscillator frequency as follows, according to the settings of the SAM1 and SAM2 pins:

| SAM2             | L           | L           | Н                  | Н                  |  |  |

|------------------|-------------|-------------|--------------------|--------------------|--|--|

| SAM1             | L           | Н           | L                  | Н                  |  |  |

| f <sub>sam</sub> | fosc<br>512 | fosc<br>288 | <u>fosc</u><br>256 | <u>fosc</u><br>224 |  |  |

|                  | (4.0kHz)    | (7.1kHz)    | (8.0kHz)           | (9.1kHz)           |  |  |

Note: Sampling frequencies in parentheses are measured at an oscillator frequency of 2.048 MHz.

If the sampling frequency during playback is varied from fsam during recording, fast and slow playback are possible. In this case, the sound level is also varied.

Example:

Sampling frequency during recording: 8.0kHz

Sampling frequency during playback:

7.1kHz: SI 9.1kHz: Fa

Slow playback Fast playback

#### 3. Use of channels

Set the RSEL1 and RSEL2 input pins according to the number of 1Mbit serial voice registers connected to the LSI (see the table below).

| RSEL2                  | L | L | Н | Н |

|------------------------|---|---|---|---|

| RSEL1                  | L | Н | Ł | Н |

| Number of              | 1 | 2 | 3 | 4 |

| serial voice registers |   |   |   |   |

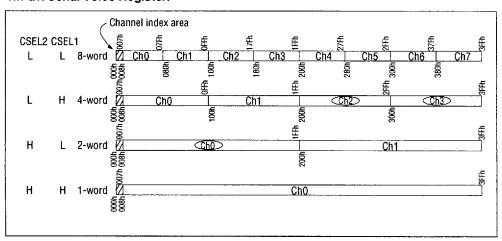

The number of the phrases to be recorded can be set to 1, 2, 4, or 8 according to the setting of the CSEL1 and CSEL2 input pins. (When three external serial voice registers are used, the phrase count can be set to 1, 2, 3, or 6.)

The memory capacity of the external serial voice registers available to each channel equals the total available memory divided by the number of phrases being recorded. IE: When the phrase count is set to 8, for example, one-eighth of the entire memory capacity is assigned as the memory capacity of each channel, and when the phrase count

is 4, one-fourth of the entire memory capacity is assigned. (The memory capacity divided and assigned to each channel is called the channel memory capacity.)

Each channel memory capacity can be assigned to a particular channel by the CA1, CA2, and CA3 input pins.

The relationships between the number of external serial voice registers used, the number of phrases to be recorded, channels, and channel memory capacities are shown in the following table.

| CSEL<br>2 | CSEL<br>1 | Number of phrases    |              |     |     |     | Channel              |              | Channel memory capacity (bit) |              |              |               |

|-----------|-----------|----------------------|--------------|-----|-----|-----|----------------------|--------------|-------------------------------|--------------|--------------|---------------|

|           |           | 1,2, or 4<br>(Note1) | 3<br>(Note1) | CA3 | CA2 | CA1 | 1,2, or 4<br>(Note1) | 3<br>(Note1) | 1<br>(Note1)                  | 2<br>(Note1) | 3<br>(Note1) | 4<br>(Note1)  |

| L         | L         | 8                    | 6            | L   | L   | L   | * *ch0               | ch0          |                               |              |              |               |

|           |           |                      |              | L   | L   | Н   | * *ch1               | ch1          |                               |              |              |               |

|           |           |                      |              | L   | Н   | L   | * ch2                | ch2          |                               |              |              |               |

|           |           |                      |              | L   | Н   | н   | * ch3                | ch3          | 128K                          | 256K         | 512K         |               |

|           |           |                      |              | Н   | L   | L   | ch4                  | ch4          | (4 s)                         | (8 s)        | (16          | S s)          |

|           |           |                      |              | Н   | L   | н   | ch5                  | ch5          |                               |              |              |               |

|           |           |                      |              | н   | н   | L   | ch6                  | ch4          |                               |              |              |               |

|           |           |                      |              | Н   | н   | н   | ch7                  | ch5          |                               |              |              |               |

| L H       |           | 4 3                  |              | L   | L   |     | * *ch0               | ch0          |                               |              |              |               |

|           |           |                      |              | L   | н   |     | * ch1                | ch1          | 256K                          | 512K         | 1M           |               |

|           | H         |                      | 3            | н   | L   | _   | ch2                  | ch2          | (8 s)                         | (16 s)       | (32 s)       |               |

|           |           |                      |              | H   | н   |     | ch3                  | ch2          | :                             |              |              |               |

|           |           |                      | -            | L   |     |     | * cl                 | 10           | 512K                          | 1M           | 1536K        | 2M            |

| Н         | L         |                      | 2            | Н   | -   | _   | ch1                  |              | (16 s)                        | (32 s)       | (50 s)       | (65 s)        |

| Н         | Н         |                      | 1            | -   | _   | _   | cl                   | 10           | 1M<br>(32 s)                  | 2M<br>(65 s) | 3M<br>(98 s) | 4M<br>(131 s) |

Note: The number of seconds in parentheses is a recording time measured at f<sub>sam</sub>=8.0kHz.

The first 8Kbit of the serial voice registers are allocated as a channel index area.

Therefore, the channel memory capacity of channel "O" is 8Kbit less than the value listed in the table above.

- 1) Number of external serial voice registers

- 2) When 512Kbit serial voice registers use, only can use (\*) (\*\*) mark channel

- 3) When 256Kbit serial voice registers use, only can use (\*\*) mark channel

# Allocation for Channel and Channel Memory Capacity in Using 1 Piece of 1M-Bit Serial Voice Register.

Note: By the combination of CSEL1, CSEL2, CA1, CA2 and CA3, the circled channel memory capacities can be allocated as Ch0=16sec., Ch2=8 sec. and Ch3=8 sec. (@f<sub>sam</sub>=8kHz).

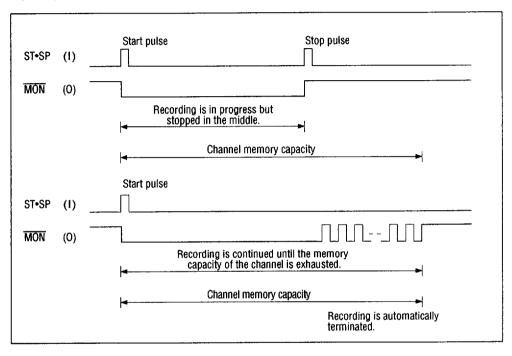

### 4. Recording

Pull the REC/PLAY pin high. Then, select the number of the phrase to be recorded with the CSEL1 and CSEL2 input pins and select a channel with the CA1 to CA2 input pins.

To stop recording in the middle of a phrase, input a pulse to the ST.SP pin again. The

recording duration is the time between these two pulses.

When recording is initiated by inputting a pulse to the ST.SP pin, and continued until the memory capacity of the specified channel is exhausted, recording is automatically terminated.

During recording, the  $\overline{MON}$  pin is low.

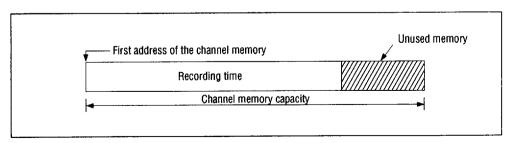

Note: As mentioned above, the memory capacity of the external serial registers is divided by the number of phrases and is assigned as the channel memory capacity. During recording, ADPCM data is written, starting from the first address of the memory of the specified channel. When recording is terminated in the middle of the channel memory capacity by a stop pulse, the subsequent memory area remains unused.

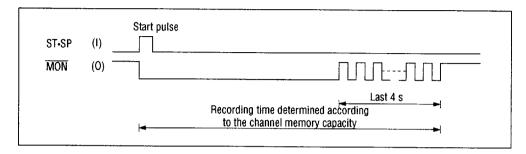

# 5. Alarm for remaining recording time

When recording is initiated by inputting a pulse to the ST•SP pin and the available

recording time reaches the last four seconds, the MON pin outputs a 4Hz clock for the last seconds as an "out of available memory" alarm.

Note: During the last four seconds a clock frequency of 4 Hz described above is output, when the sampling frequency (f<sub>sam</sub>) of 8.0 kHz is selected. The duration of the alarm clock is proportional to the length of the cycle of the sampling frequency and the clock frequency is proportional to the sampling frequency used.

### 6. Playback

Set the REC/PLAY pin low. Then, select the number of the phrase recorded with the CSEL1 and CSEL2 input pins and select a channel with the CA1 to CA3 input pins. To initiate playback, input a pulse to the ST•SP pin. Playback is automatically stopped when the recording time is expired.

To stop playback in the middle of a phrase,

input a pulse to the ST•SP pin again.

During playback, the MON pin is kept low.

Do not start playback in channels not recorded because the playback data and time are undefined.

However, playback under these conditions can be halted by a stop pulse.

Playback can be repeated by maintaining the ST•SP pin high.

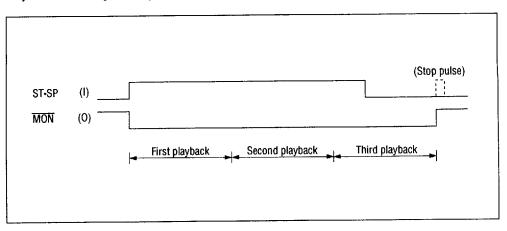

# 7. Debounce circuit for the ST.SP pin

A debounce circuit functions to prevent the ST.SP pin from malfunctioning due to switch

contact bounce. The debounce time is 32 ms. Be sure to set the time during which the ST.SP pin is kept high for at least 70 ms.

# Operations in the microcontroller interface application

The MSM6388 LSI operations are controlled by pins 2VCK, MCK, PD and 16 commands using pins D0 to D3,  $\overline{WR}$  and  $\overline{RD}$ .

# 1. Explanation of Commands

| Command   | Code   |        |        |        |                                                                             |  |

|-----------|--------|--------|--------|--------|-----------------------------------------------------------------------------|--|

| Command   | D<br>3 | D<br>2 | D<br>1 | D<br>0 | Function                                                                    |  |

| NOP       | 0      | 0      | 0      | 0      | (NON OPERATION) Has no particular function but is used during               |  |

|           |        |        |        |        | execution of a EPLAY or EREC command.                                       |  |

| INIT      | 0      | 0      | 0      | 1      | ( <u>INIT</u> IALIZE)                                                       |  |

|           |        |        |        |        | Writes the last address of the external serial voice regisrers as the start |  |

|           |        |        |        |        | and stop addresses of each of channels 0 to 7 to set the channel            |  |

|           |        |        |        |        | memory in the unrecorded state.                                             |  |

|           |        |        |        |        | Sets channel 0 in the channel register.                                     |  |

| PLAY      | 0      | 0      | 1      | 0      | (PLAY BACK) Set the playback mode.                                          |  |

| REC       | 0      | 0      | 1      | 1      | (RECORD) Set the recording mode.                                            |  |

| START     | 0      | 1      | 0      | 0      | (START) Starts recording or playback. At the same time, it writes the       |  |

|           |        |        |        |        | start and stop addresses stored in the channel index area into the LSI.     |  |

| STOP STOP | 0      | 1      | 0      | 1      | (STOP) Stops recording or playback.                                         |  |

|           |        |        |        |        | When this command is executed during recording, it stores the contents      |  |

|           |        |        |        |        | of the address counter at the stop time in the channel index area           |  |

|           |        |        |        |        | as the stop address.                                                        |  |

| SAMP      | 0      | 1      | 1      | 0      | (SAMPLING FREQUENCY) Specifies a sampling frequency together                |  |

|           |        |        |        |        | with the next nibble.                                                       |  |

| CHAN      | 0      | 1      | 1      | 1      | (CHANNEL) Specifies a channel together with the next nibble.                |  |

| STWR      | 1      | 0      | 0      | 0      | (START ADDRESS WRITE) Stores the start address in the channel index         |  |

|           |        |        |        |        | area together with the next three nibbles.                                  |  |

| SPWR      | 1      | 0      | 0      | 1      | (STOP ADDRESS WRITE) Stores the stop address in the channel index           |  |

|           |        |        |        |        | area together with the next three nibbles.                                  |  |

| STRD      | 1      | 0      | 1      | 0      | (START ADDRESS READ) Reads the start address stored in the channel          |  |

|           |        |        |        |        | index area through the next three read accesses. During this operation,     |  |

|           |        |        |        |        | the contents of the status register cannot be read.                         |  |

| SPRD      | 1      | 0      | 1      | 1      | (STOP ADDRESS READ) Reads the stop address stored in the channel            |  |

|           |        |        |        |        | index area through the next three read accesses. During this operation,     |  |

|           |        |        |        |        | the contents of the status register cannot be read.                         |  |

|         | Code               |   |        |          |                                                                                                                                                                                                    |  |

|---------|--------------------|---|--------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Command | D D D D<br>3 2 1 0 |   | D<br>0 | Function |                                                                                                                                                                                                    |  |

| DTRD    | 1                  | 1 | 0      | 0        | (DATA READ) Reads the contents of external serial voice registers 1K bit sequentially through the data bus on the specified timing. When this command is issued, the LSI enters the playback mode. |  |

| DTWR    | 1                  | 1 | 0      | 1        | (DATA WRITE) Writes data into external serial voice registers 1 Kbit sequentially through the data bus on the specified timing. When this command is issued, the LSI enters the recording mode.    |  |

| EPLAY   | 1                  | 1 | 1      | 0        | (EXTERNAL PLAYBACK) Plays back ADPCM data while reading it from the data bus on the specified timing. When this command is issued, the LSI enters the playback mode.                               |  |

| EREC    | 1                  | 1 | 1      | 1        | (EXTERNAL RECORDS) Starts recording and outputs ADPCM data to the data bus on the specified timing. When this command is issued, the LSI enters the recording mode.                                |  |

# • MSM6388 Commands

| Command | First nibble command D D D D D D 3 2 1 0 | Second nibble command D D D D D 3 2 1 0 | Third nibble<br>command<br>D D D D<br>3 2 1 0 | Fourth nibble command D D D D D 3 2 1 0 |

|---------|------------------------------------------|-----------------------------------------|-----------------------------------------------|-----------------------------------------|

| NOP     | 0 0 0 0                                  |                                         |                                               |                                         |

| INIT    | 0 0 0 1                                  |                                         |                                               |                                         |

| PLAY    | 0 0 1 0                                  |                                         |                                               |                                         |

| REC     | 0 0 1 1                                  |                                         |                                               |                                         |

| START   | 0 1 0 0                                  |                                         |                                               |                                         |

| STOP    | 0 1 0 1                                  |                                         |                                               |                                         |

| SAMP    | 0 1 1 0                                  | - S2 S1 S0                              |                                               | <u> </u>                                |

| CHAN    | 0 1 1 1                                  | - C2 C1 C0                              |                                               |                                         |

| STWR    | 1 0 0 0                                  | A3 A2 A1 A0                             | A7 A6 A5 A4                                   | A11 A10 A9 A8                           |

| SPWR    | 1 0 0 1                                  | A3 A2 A1 A0                             | A7 A6 A5 A4                                   | A11 A10 A9 A8                           |

| STRD    | 1 0 1 0                                  | A3 A2 A1 A0                             | A7 A6 A5 A4                                   | A11 A10 A9 A8                           |

| SPRD    | 1 0 1 1                                  | A3 A2 A1 A0                             | A7 A6 A5 A4                                   | A11 A10 A9 A8                           |

| DTRD    | 1 1 0 0                                  |                                         |                                               |                                         |

| DTWR    | 1 1 0 1                                  | Operates on the specified timing.       |                                               |                                         |

| EPLAY   | 1 1 1 0                                  |                                         |                                               |                                         |

| EREC    | 1 1 1 1                                  |                                         |                                               |                                         |

# • Sampling frequency specification (SAMP command)

| S2 | <b>S</b> 1 | S0 |      | Sampling frequency |          |

|----|------------|----|------|--------------------|----------|

| 0  | 0          | 0  | SA0  | fosc/576           | (3.6kHz) |

| 0  | 0          | 1  | SA1  | fosc/512           | (4.0kHz) |

| 0  | 1          | 0  |      |                    |          |

| 0  | 1          | 1  | SA2  | fosc/448           | (4.6kHz) |

| 1  | 0          | 0  | SA3  | fosc/288           | (7.1kHz) |

| 1  | 0          | 1  | SA4  | fosc/256           | (8.0kHz) |

| 1  | 1          | 0  | 0.4- |                    |          |

| 1  | 1          | 1  | SA5  | fosc/224           | (9.1kHz) |

Note: Frequencies in parentheses are used when the oscillator frequency  $f_{OSC}$  is 2.048MHz.

# • Channel specification

| C2 | <b>C</b> 1 | CO | Channel |

|----|------------|----|---------|

| 0  | 0          | 0  | ChO     |

| 0  | 0          | 1  | Ch1     |

| 0  | 1          | 0  | Ch2     |

| 0  | 1          | 1  | Ch3     |

| 1  | 0          | 0  | Ch4     |

| 1  | 0          | 1  | Ch5     |

| 1  | 1          | 0  | Ch6     |

| 1  | 1          | 1  | Ch7     |

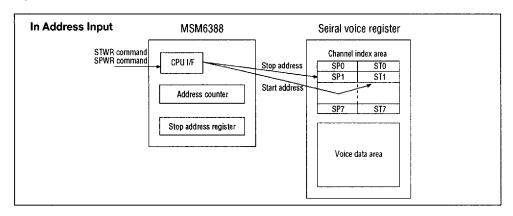

Start and stop addresses (STWR, SPWR, STRD, and SPRD commands)

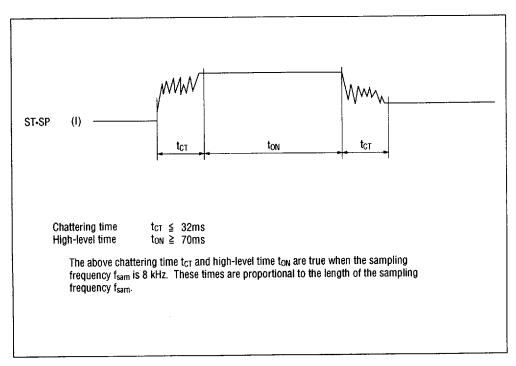

The start and stop addresses used to control recording time is managed by 12bit. The available memory capacity varies depending on the number of serial voice registers to be connected externally.

Regardless of the number of serial voice registers, the area between addresses 000H

and 007H is allocated as the channel index area to store the start and stop addresses for each channel. The area starting from address 008H can be used to store voice data (ADPCM data).

When on use 512Kbit serial voice register, can use  $008H \sim 1FF$  address.

When on use 256K serical voice register, can use 008H~0FF address.

#### 2. Explanation of the status register

The status register consists of three bits. When a negative-going pulse is supplied to the /RD pin, the status of these bits is output to  $D0 \sim D2$ . Note that the status is not output

during the execution of an STRD or SPRD command. During execution of a DTRD, DTWR, EPLAY, or EREC command, Status must be read only when the timing is correct.

| D3  | D2    | D1    | D0   |

|-----|-------|-------|------|

| "L" | DTMNT | RPMNT | BUSY |

#### (1) Busy

The busy bit is high when the LSI is being initialized or when it is executing a command.

When the busy bit is high, do not issue a command from the microcomputer.

#### **BUSY Timing**

| BUSY con-                         | BUSY time max.                                             |                            |

|-----------------------------------|------------------------------------------------------------|----------------------------|

| NOP, PLAY, REC, START, STOP comma | 4/f <sub>sam</sub> (500μs)<br>34/f <sub>sam</sub> (4.75ms) |                            |

| INIT command                      |                                                            |                            |

|                                   | First nibble                                               | 4/fsam (500µs)             |

| SAMP, CHAN command                | Second nibble                                              | 4/f <sub>sam</sub> (500µs) |

|                                   | First nibble                                               | 6/f <sub>sam</sub> (750µs) |

| STWR, SPWR command                | After second nibble                                        | 4/f <sub>sam</sub> (500µs) |

| OTDD 0000                         | First nibble                                               | 6/f <sub>sam</sub> (750µs) |

| STRD, SPRD command                | After second nibble                                        | 4/f <sub>sam</sub> (500µs) |

Note: The inside of parentheses shows the time of f<sub>sam</sub>=8kHz.

BUSY time is porportional to f<sub>sam</sub> frequency.

(2) RPMNT (Record Playback MoNiTor)

The RPMNT bit is high when the LSI is recording or playing back data. When the RPMNT bit is high, do not input a command except the STOP command.

(3) DTMNT (Data Read Write MoNiTor)

The DTMNT bit is high when data is being transferred to or from serial voice registers by the DTRD or DTWR command.

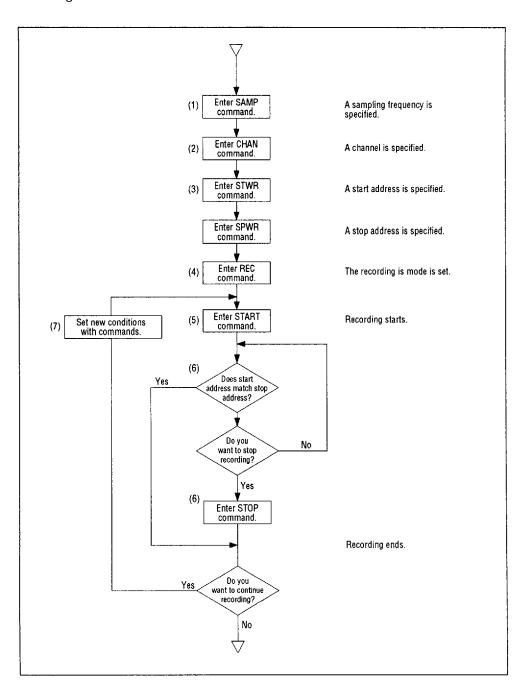

- Recording

- Sampling frequency select:

To select a sampling frequency fsam, enter a

SAMP command.

(2) Channel select:

To select a channel, enter a CHAN command. Usually, specify channel 0.

(3) Start and stop addresses select:

To allocate an area for recording voice data, enter STWR and SPWR commands to store a start address and a stop address in the specified channel field in the channel index area.

(4) To enter the recording mode, enter an REC command.

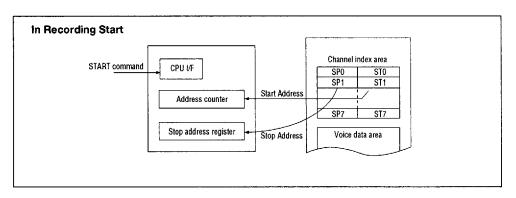

- (5) To start recording, enter a START command. The LSI fetches the start and stop addresses of the specified channel from the channel index area and stores the start address in the address counter and the stop address in the stop address register, then starts recording.

- (6) Stopping recording:

When the contents of the address counter match those of the stop address register, recording is stopped automatically. To stop recording in the middle, enter a STOP command. In this case, the contents of the ad-

dress counter at recording stop are stored in the channel index area as the stop address.

(7) To resume recording, specify new conditions with commands as described in items (1) to (3) above and follow the procedure described above.

The start and stop address of each channel can be read by STRD and SPRD commands.

When these addresses are controlled by a microcomputer, the memory capacity of external serial voice registers can be used efficiently.

### Recording Flowchart when the LSI is Interfaced with a Microcontroller

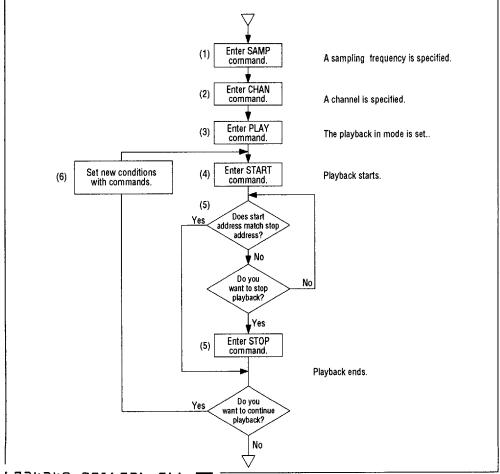

- 4. Playback

- (1) Sampling frequency select:

To select a sampling frequency, enter a SAMP command.

(2) Channel select:

To select a channel, enter a CHAN command. Usually, specify channel 0.

- (3) To enter the playback mode, enter a PLAY command.

- (4) To start playback, enter a START command. The LSI fetches the start and

stop addresses of the specified channel index area and then starts playback.

(5) Stopping playback:

When the contents of the address counter match those of the stop address register, playback is stopped automatically. To stop playback in the middle, enter a STOP command.

(6) To resume playback, specify new conditions with commands as described in items (1) and (2) above and follow the procedure described above.

Playback flowchart when the LSI is connected to a microcontroller interface

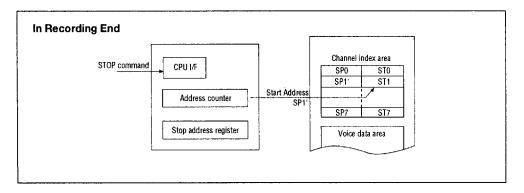

#### 5. Channel Index Area

Operation for channel index area in recording is shown below.

START address and STOP address area written to the channel that designated the channel index area by STWR and SPWR commands.

When START command is inputted, the recording is started after the start addresses of channel index area are automatically set

to respective address counter and STOP address register.

When STOP command is inputted, the contents for the address counter of that time is

automatically set to the channel index area as a new STOP address.

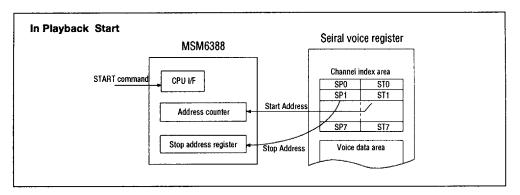

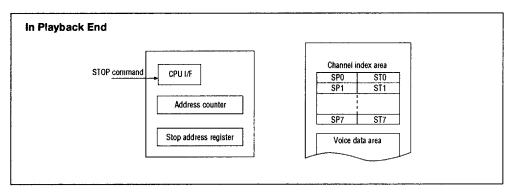

Operation for channel index area in playback is shown below.

When START command is inputted, the playback is started after the START address

and STOP address of the channel that designated the channel index area are automatically set to respective address counter and STOP address register.

When STOP command is inputted, the playback finishes. The MSM6388 does not exchange the data with the channel index area.

Recording and playback for nine or more channels

When the start and stop addresses of each channel are stored in memory in a microcontroller or external circuitry, recording and playback for nine or more channels is possible. Voice data can be recorded on the same way as for recording described in item 3 above. However, channel 0 must be set.

To play back voice data, enter a STWR command specifying the start address of the voice data area from which to start playback and a SPWR command specifying the stop address of the area to write these addresses in channel 0 field of the channel index area. When a START command is entered, the LSI fetches the start and stop addresses from the channel 0 field in the same way as for playback described in item 4 above, then starts playback.

Reading and writing data in external serial voice registers with DTRD and DTWR commands

DTRD and DTWR commands can be used to read from and write to the external serial voice registers.

To read the contents of the serial voice registers, enter an STWR command specifying a start address of the area to be read and an SPWR command specifying a stop address of the area to write these addresses in the channel index area. When a DTRD command is entered, data is read 4bit at a time during each cycle of the sampling frequency.

To write data to the serial voice registers, first write start and stop addresses then enter a DTWR command. Data is written 4bit at a time on the correct RD and WR timings.

Data transfer using DTRD and DTWR commands is performed in 1Kbit units. These two commands can be used to move voice data stored in serial voice registers to different addresses, providing a useful way to use the memory capacity of the serial voice registers.

Recording and playing back voice data through the data bus with EREC and EPLAY commands

Specify the sampling frequency with a SAMP command, and input an EREC command.

When an EREC command is entered, the LSI enters the recording mode and recording starts.

Voice data (ADPCM data) is output to the data bus on the correct  $\overline{RD}$  and  $\overline{WR}$  timings. To stop recording, enter a STOP command on the correct timing.

To perform playback, enter an EPLAY command. The LSI enters the playback mode and starts to play back voice data—the data is input from the data bus on the correct WR timing. To stop playback, enter a STOP command.

During execution of an EREC or EPLAY command, address management and external serial voice register driving are not performed.

9. Initialization by the INIT command

When an INIT command is entered, the channel memory is set in the unrecorded state.

- The INIT command writes the last address of the external serial voice registers as the start and stop addresses in individual fields of channels 0 to 7 in the channel index area. This sets the channel memory in the unrecorded state.

- The command then sets channel 0 in the channel register.

- 10. Power down function (pin PD)

When pin PD is set at the high level, the LSI enters the power down state. Note that this function is invalid during recording or playback.

- Oscillation is stopped and all operation of the internal circuitry is stopped.

- Data bus pins D0 to D3 are set in the high impedance state.

- Output pins CS1 to CS4 are set at the high level, minimizing the current required by the external serial voice registers.

| D0~D3                                                       | H~Z   |

|-------------------------------------------------------------|-------|

| SAD, <del>SAS</del> , <del>TAS</del> , <del>WE</del> , DIN, |       |

| RWCK, CS1~CS4                                               | "H"   |

| 2VCK, MCK                                                   | "L"   |

| AOUT, DAO, SGC GND                                          | level |

11. Command enable function (pin  $\overline{CE}$ )

When the pin  $\overline{CE}$  is set at the high level, the LSI enters the command enable state, rejecting  $\overline{RD}$  and  $\overline{WR}$  pulses. In this state, data bus pins D0 to D3 are set in the high impedance state.

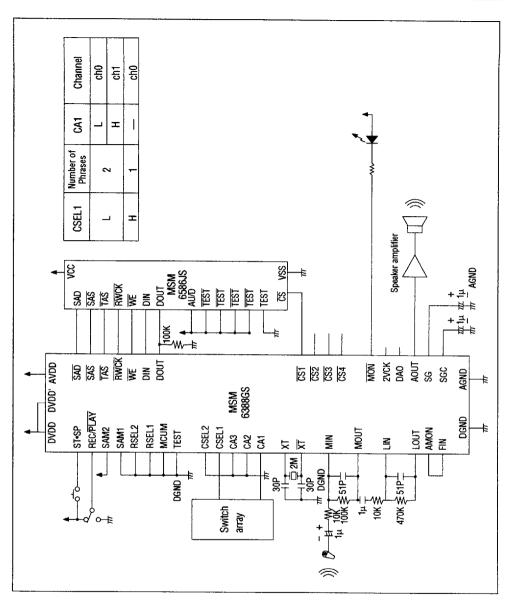

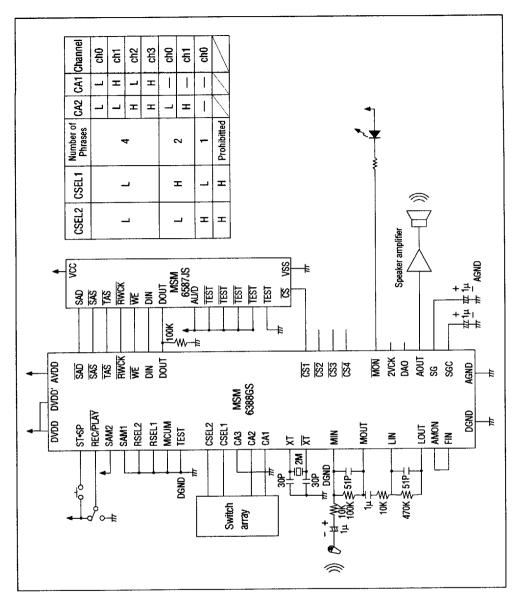

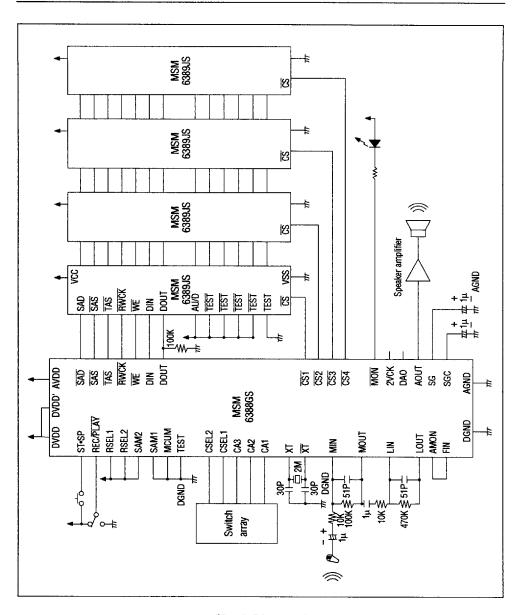

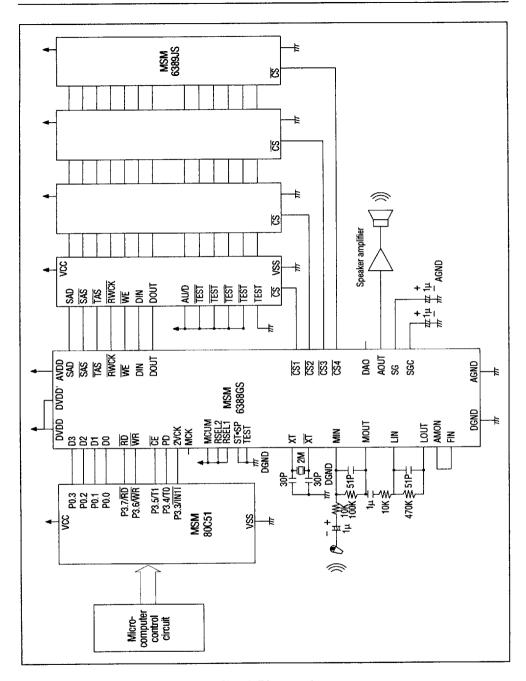

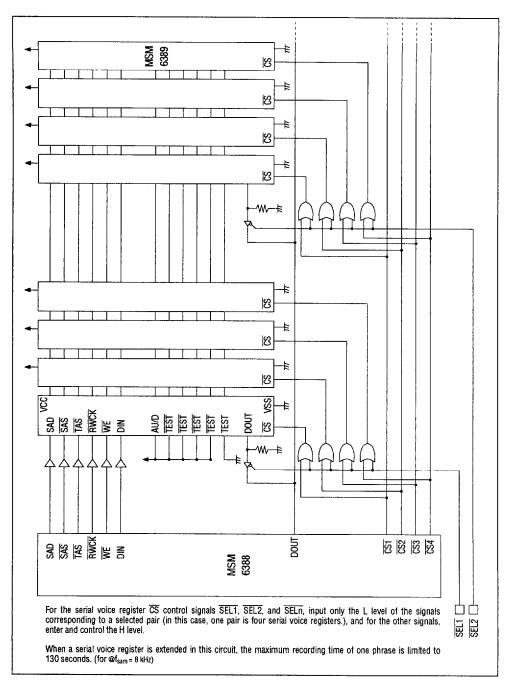

### SAMPLE APPLICATION CIRCUITS

- The circuit diagram 1 shows an example of an application's circuit with the MSM6388 and one 256Kbit serial voice register

- The circuit diagram 2 shows an example of an applications's circuit with the MSM6388 and one 512Kbit serial voice register.

- The circuit diagram 3 shows an example of an application's circuit with

- the MSM6388 and four 1Mbit serial voice registers.

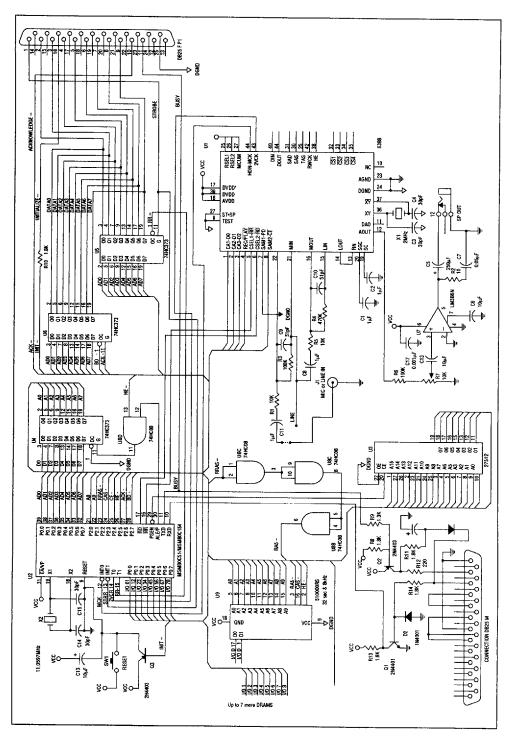

- Circuit diagram 4 shows an example of the interface with the MSM80C51 when the MSM6388 is used with a microcomputer interface.

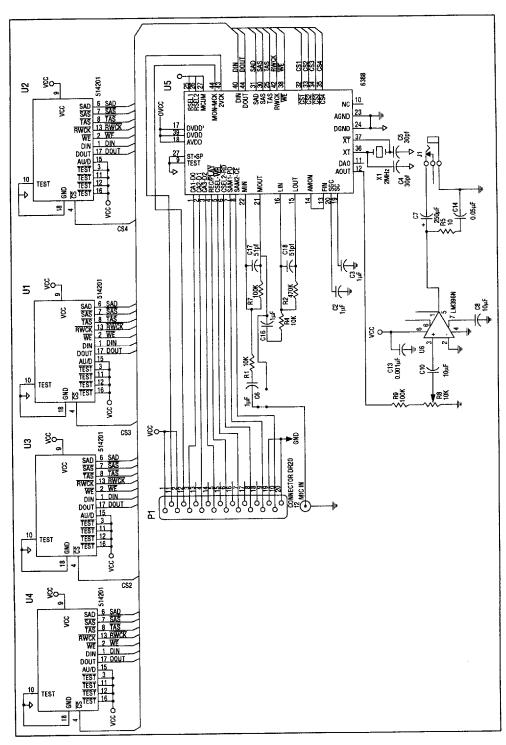

- Circuit diagram 5 shows an example of an application using greater than 4-1Mbit serial voice register's with the MSM6388.

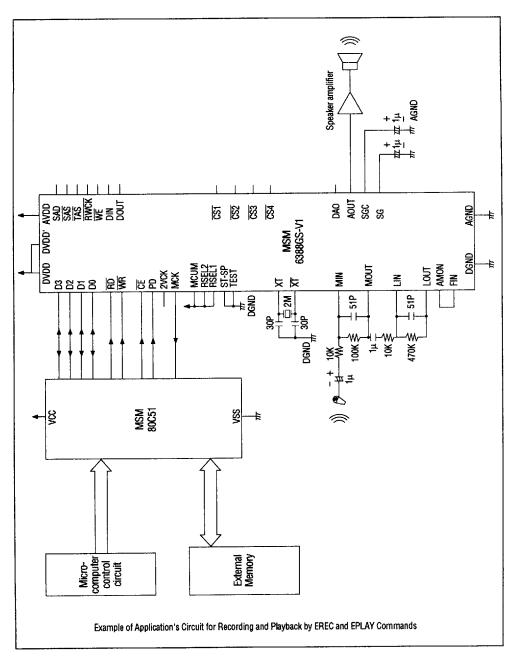

- Circuit diagram 6 shows an example of an application's circuit for recording and playback by the EREC and EPLAY commands of the MSM6388.

Circuit Diagram 1

Circuit Diagram 2

558

Circuit Diagram 3

Circuit Diagram 4

Circuit Diagram 5

Circuit Diagram 6

MSM6388 with 80C154 and DRAMS

MSM6388 Development System

**■** 6724240 0016748 488 **■**